posted by sakurai on June 7, 2021 #414

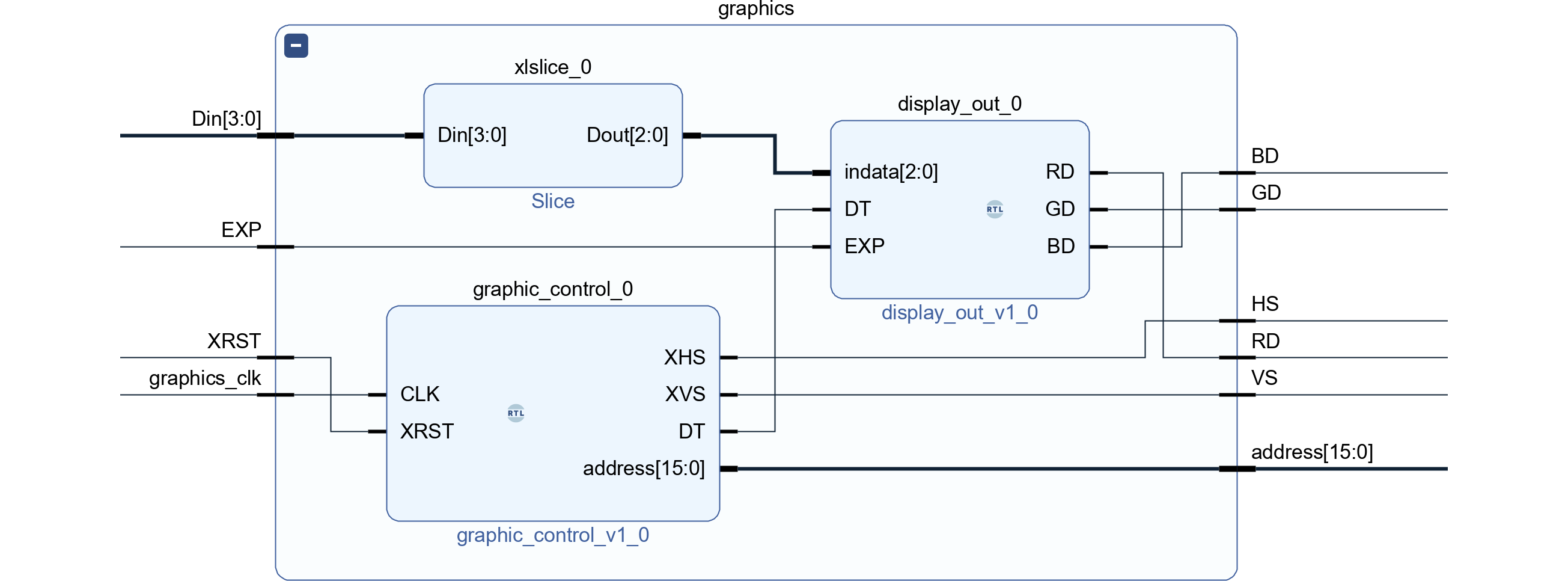

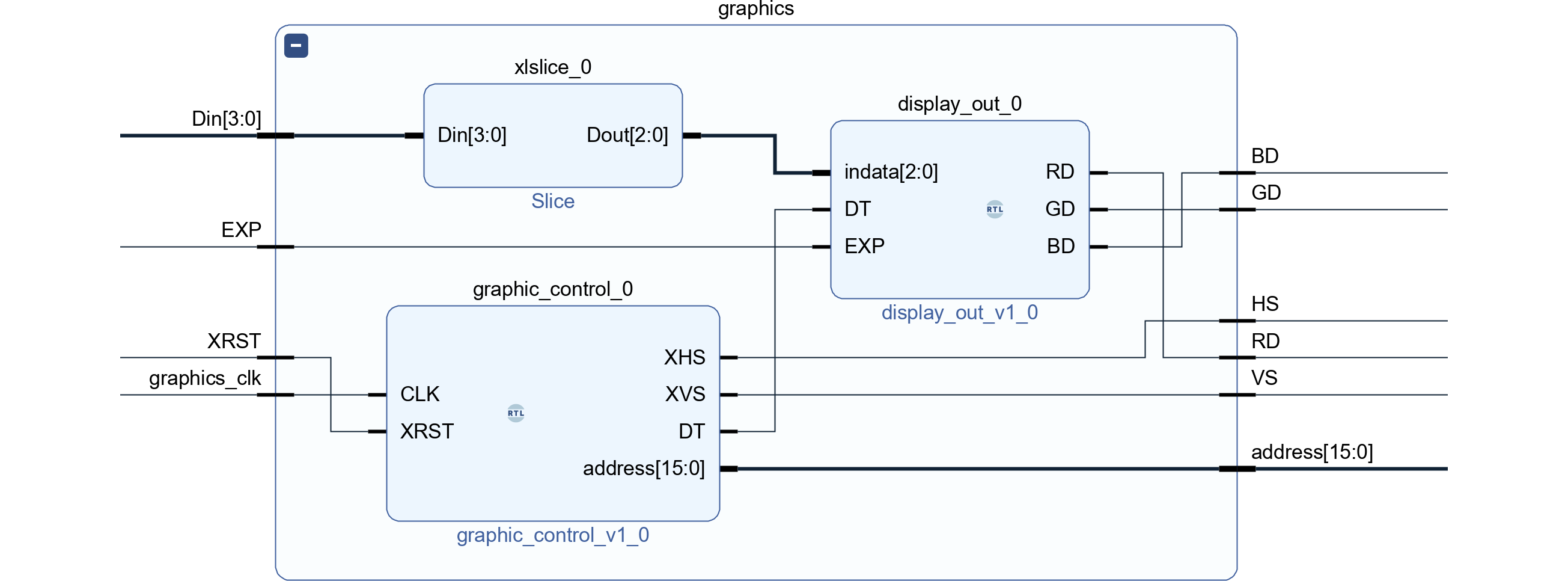

graphics階層

基本的にはgraphic_controlモジュールが中心となる階層です。次の3つのモジュールから構成されています。

- graphic_controlモジュール --- クロックとリセットを入力し、HS, VS, DT等のグラフィックディスプレイタイミングやVRAMアドレスを生成するモジュール (Verilog)

xslice --- VRAMデータ中のRGB成分のみを抜き出す (Xilinx IP)。VRAMはRGBの他にもう一面持っており、その面にはシールドデータのみが描画されています。しかしながら、その面は表示はされません。この情報は、自弾及び敵弾の衝突判定に用います。これによりシールドをピクセル毎に破壊することができます。

図414.1 ピクセル毎の衝突判定

図414.1 ピクセル毎の衝突判定display_outモジュール --- ディスプレイタイミング時に表示データを出力し、さらに爆発信号EXPにより全面赤表示にするモジュール (Verilog)

図414.2 graphics階層

図414.2 graphics階層

前のブログ

次のブログ

前のブログ

次のブログ

posted by sakurai on June 4, 2021 #413

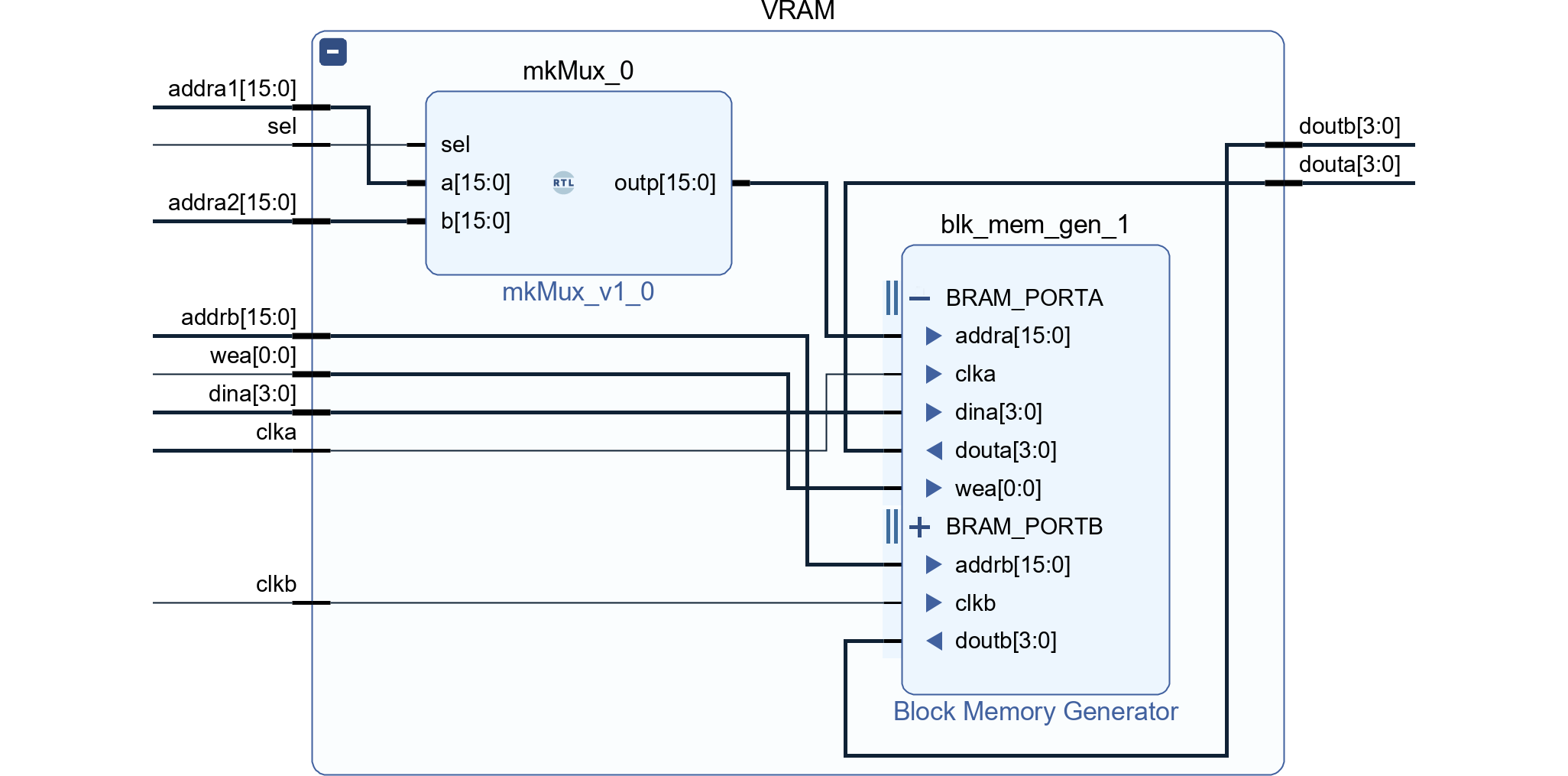

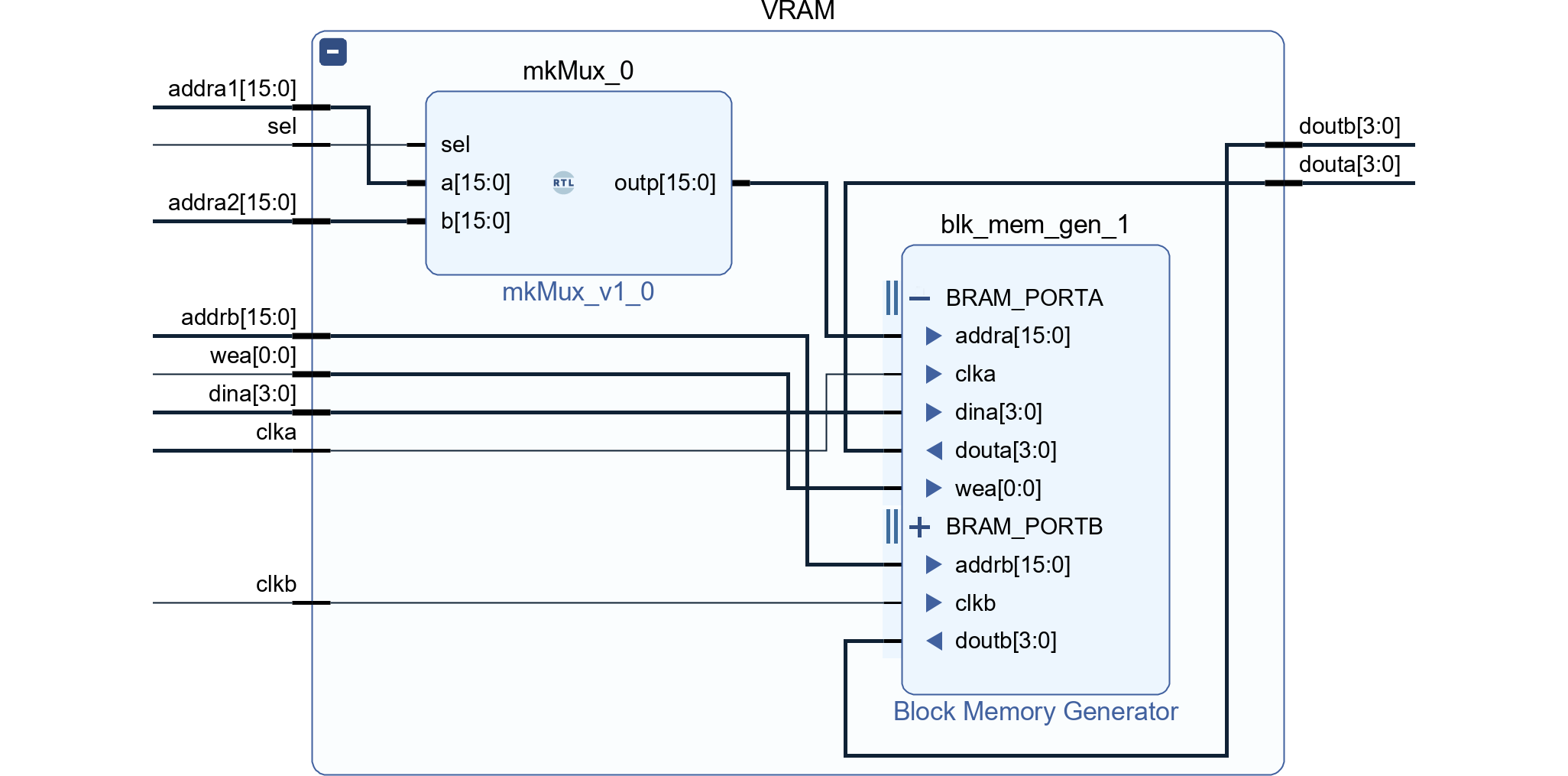

VRAM階層

VRAM階層は、図413.1で示すように以下の2モジュールから構成されます。

- VRAM --- 256×256×4bitのデュアルポートメモリ (Xilinx IP)

- Muxモジュール --- メモリダンプモジュールからのアドレスをマルチプレクスする (BSV⇒Verilog, 過去記事で設計)

図413.1 VRAM階層

図413.1 VRAM階層

前のブログ

次のブログ

前のブログ

次のブログ

posted by sakurai on June 3, 2021 #412

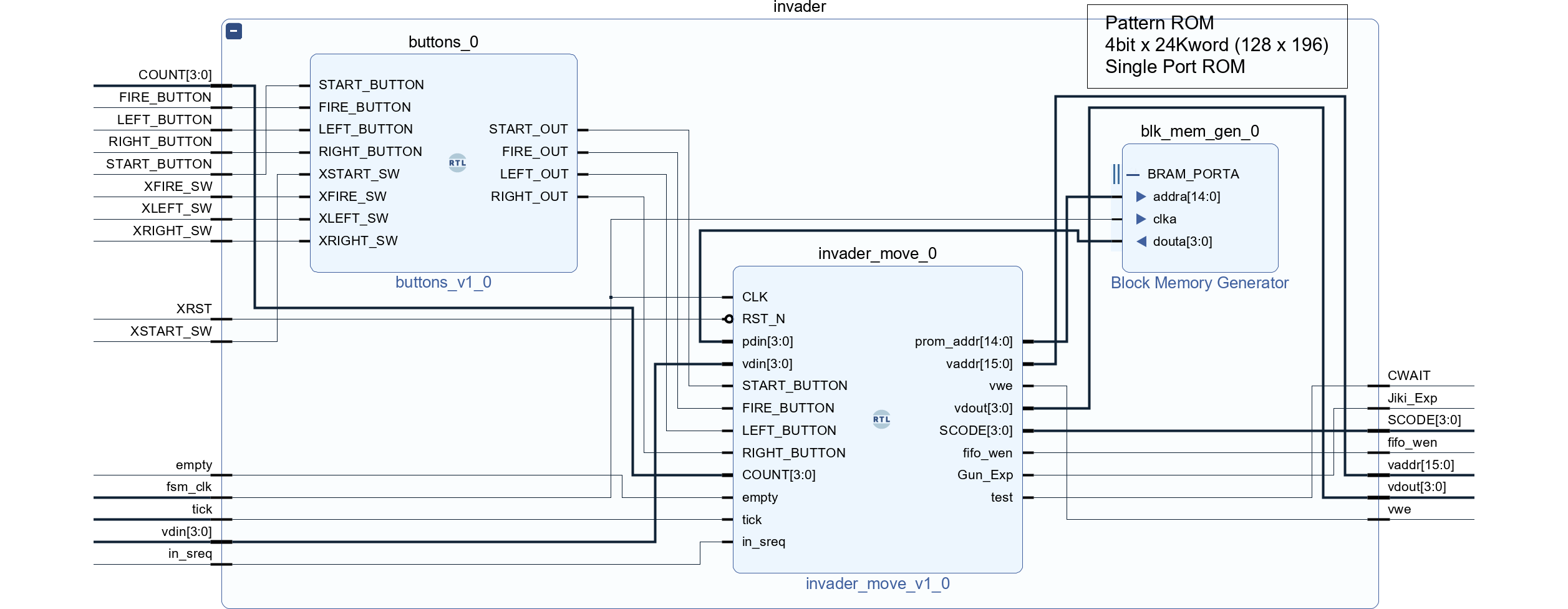

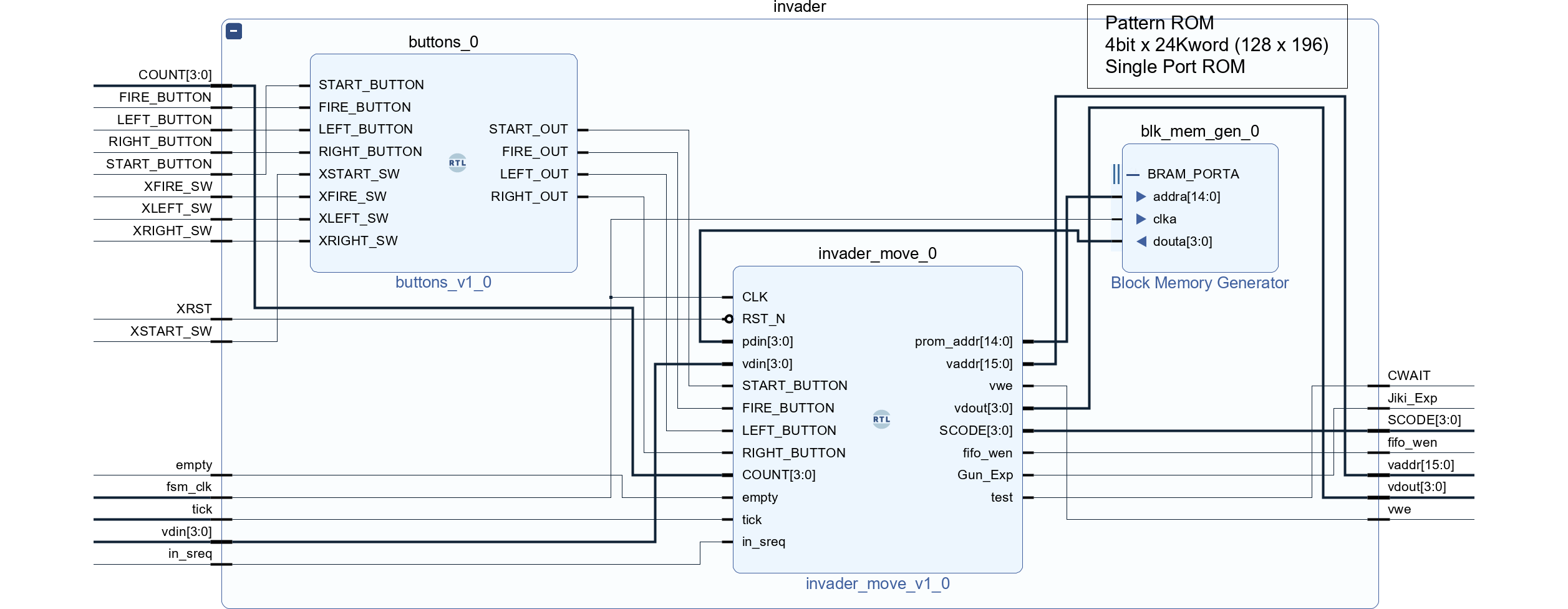

invader階層

引き続きinvader階層です。これはインベーダゲームの中心となる、GameFSM(invader_move)を含む階層です。基本的には、

- GameFSMモジュール --- ゲームのシナリオを実行するFSM (BSV⇒Verilog)

- パターンROM --- インベーダその他のビットマップを格納するROM (Xilinx IP)

の2つのモジュールにより、VRAMをR/Wすることにより絵を動かしています。この階層には、さらに以下のモジュールが存在します。

- buttonsモジュール --- FPGAボード上のプッシュボタンと、PMODのジョイスティックインタフェースのOR取り (Verilog)

図412.1 invader階層

図412.1 invader階層

前のブログ

次のブログ

前のブログ

次のブログ

posted by sakurai on June 2, 2021 #411

ソフトブロック解説

ここから、簡単に各ソフトブロック階層の解説をします。全体ブロック図は過去記事に挙げてあります。全体ブロック図において、左から順に、clock階層、メモリダンプモジュール(ソフトブロック階層無し)、invader階層、VRAM階層、graphics階層、sound階層となっています。

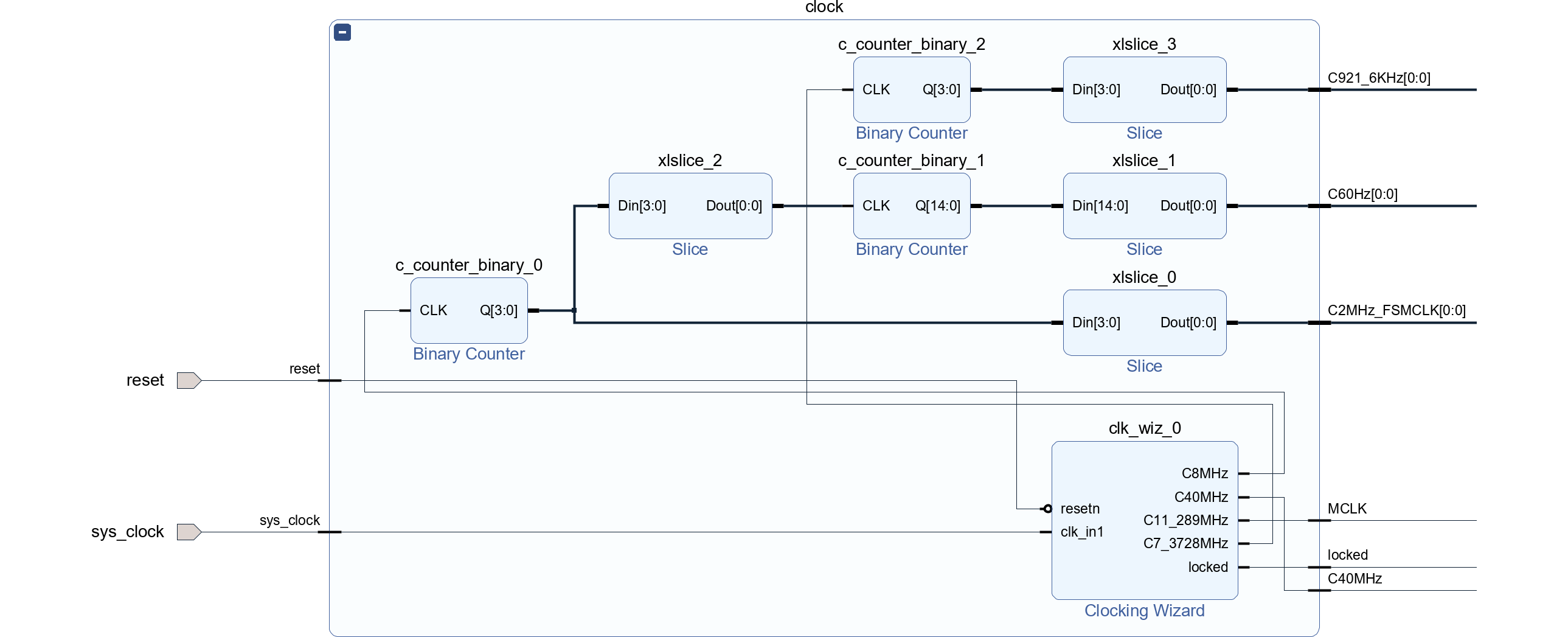

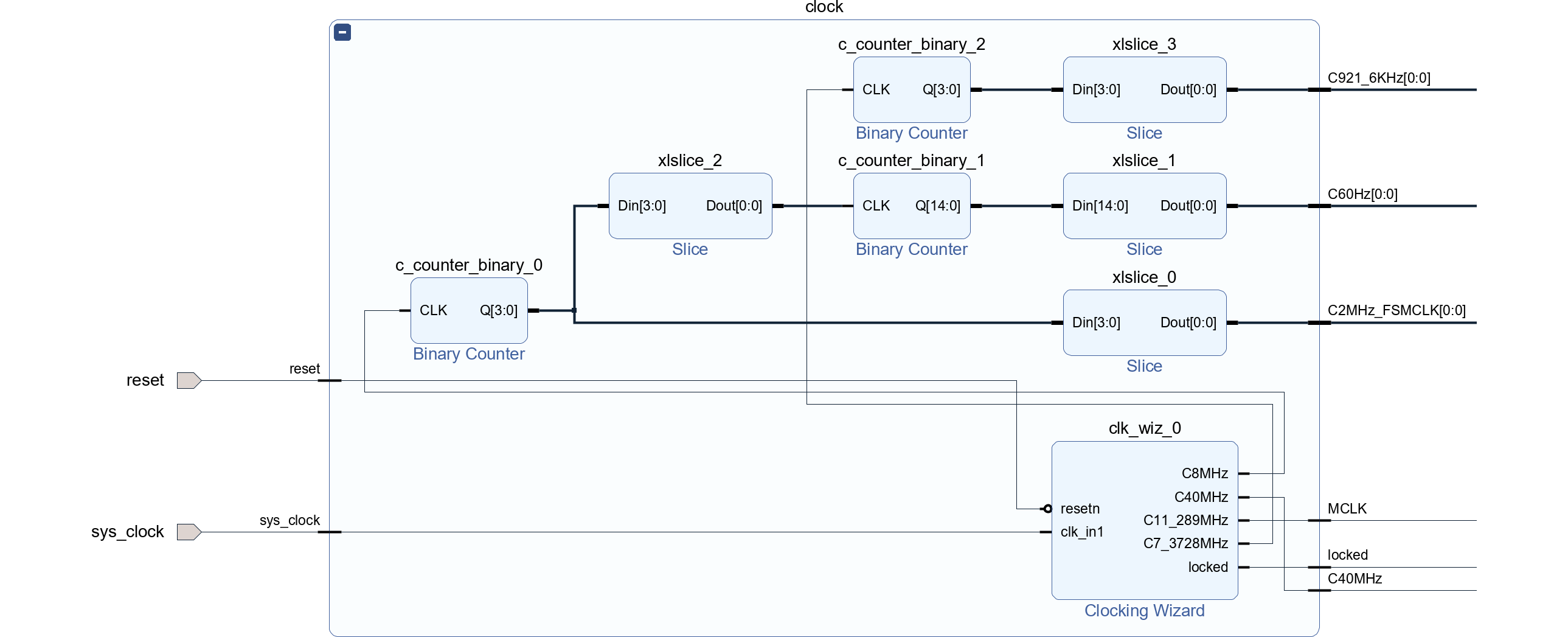

clock階層

図411.1にclock階層の構造を示します。使用されているモジュールは全てXilinx IPです。

図411.1 clock階層

図411.1 clock階層

入力は

- sys_clock --- 100MHzクロック

- reset --- 負論理リセット

の2本です。出力は、

- C921_6KHz --- 921.6KHzクロックであり、UARTのボーレートクロック

- C60Hz --- 60Hzクロックであり、動画の1フレーム(tick)を決める基準クロック

- C2MHz_FSMCLK --- 文字通り2MHzのFSMクロック

- MCLK --- 11.289MHzクロックであり、サウンド用のマスタークロック

- C40MHz --- 40MHzクロックであり、グラフィックのドットクロック

- locked --- 負論理のリセット信号

バイナリカウンタ説明

- c_counter_binary_0 --- clk_wizからの8MHzクロックを入力し、bit0(4MHz)、bit1(2MHz)、bit2(1MHz)と分周する。xslice_0はそのbit1(2MHz)を取り出し、C2MHz_FSMCLKとして出力する。

- c_counter_binary_1 --- c_counter_binary_0からxslice_2はそのbit2(1MHz)を取り出し、c_counter_binary_1で0x411a(=16666)を計数したらリセットする。xslice_1ではその14bit(16.667msec=59.9988Hz)を取り出し、C60Hzとして出力する。これはデューティは50%ではないが、エッジを見るため問題ない。

- c_counter_binary_2 --- clk_wizからの7.3728MHzクロックを入力し、bit0(3.6864MHz)、bit1(1.8432MHz), bit2(921.6KHz)と分周する。xslice_3はそのbit2(921.6KHz)を取り出しC921_6KHzとして出力する。

スライス値

- xslice_0 --- 4,1,1,1

- xslice_1 --- 15,14,14,1

- xslice_2 --- 4,2,2,1

- xslice_3 --- 4,2,2,1

前のブログ

次のブログ

前のブログ

次のブログ

posted by sakurai on June 1, 2021 #410

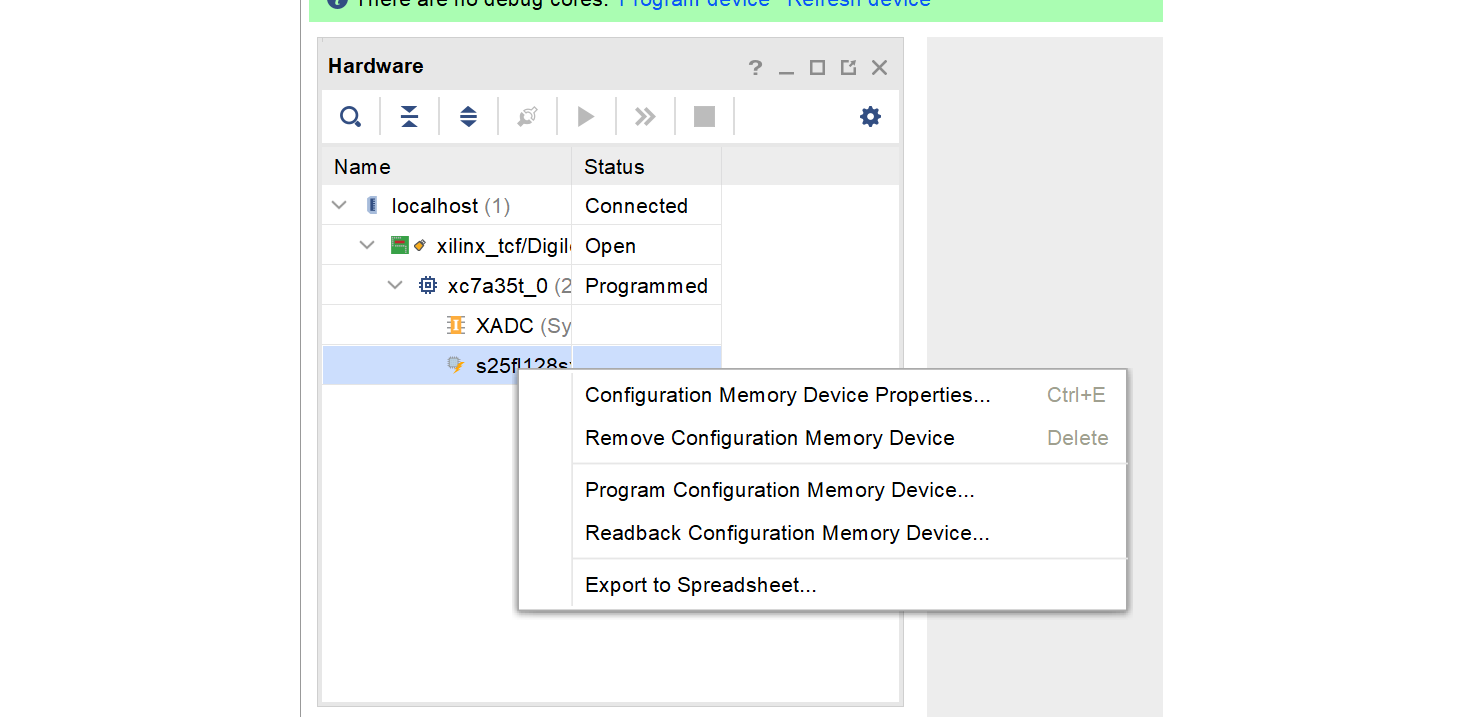

QSPIへの再書き込み

Artyボードにおいて、基本的には過去記事で示した手順でFlashに書き込みます。ところが、一度Flashに書き込むと、Add Configuration Memory Deviceがグレーアウトされていることがあります。その場合は、

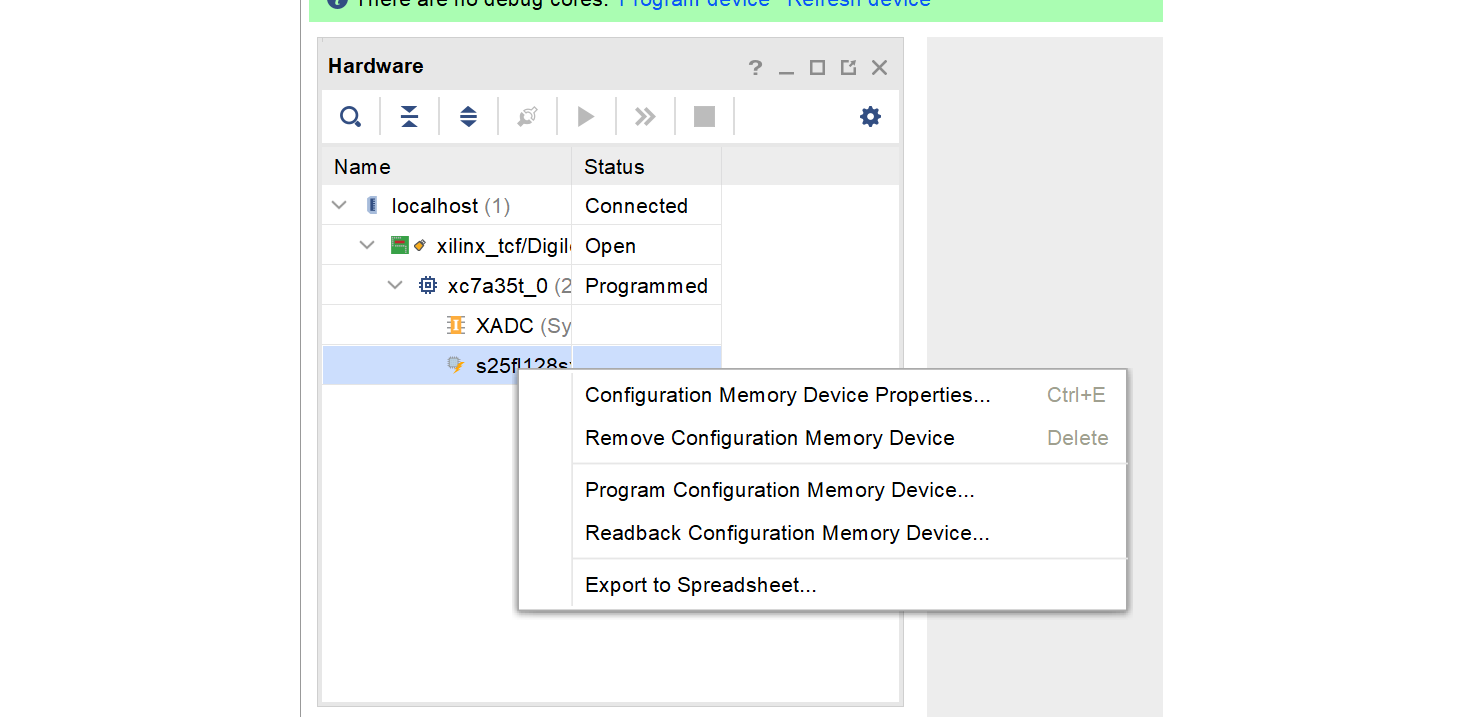

図410.1

図410.1

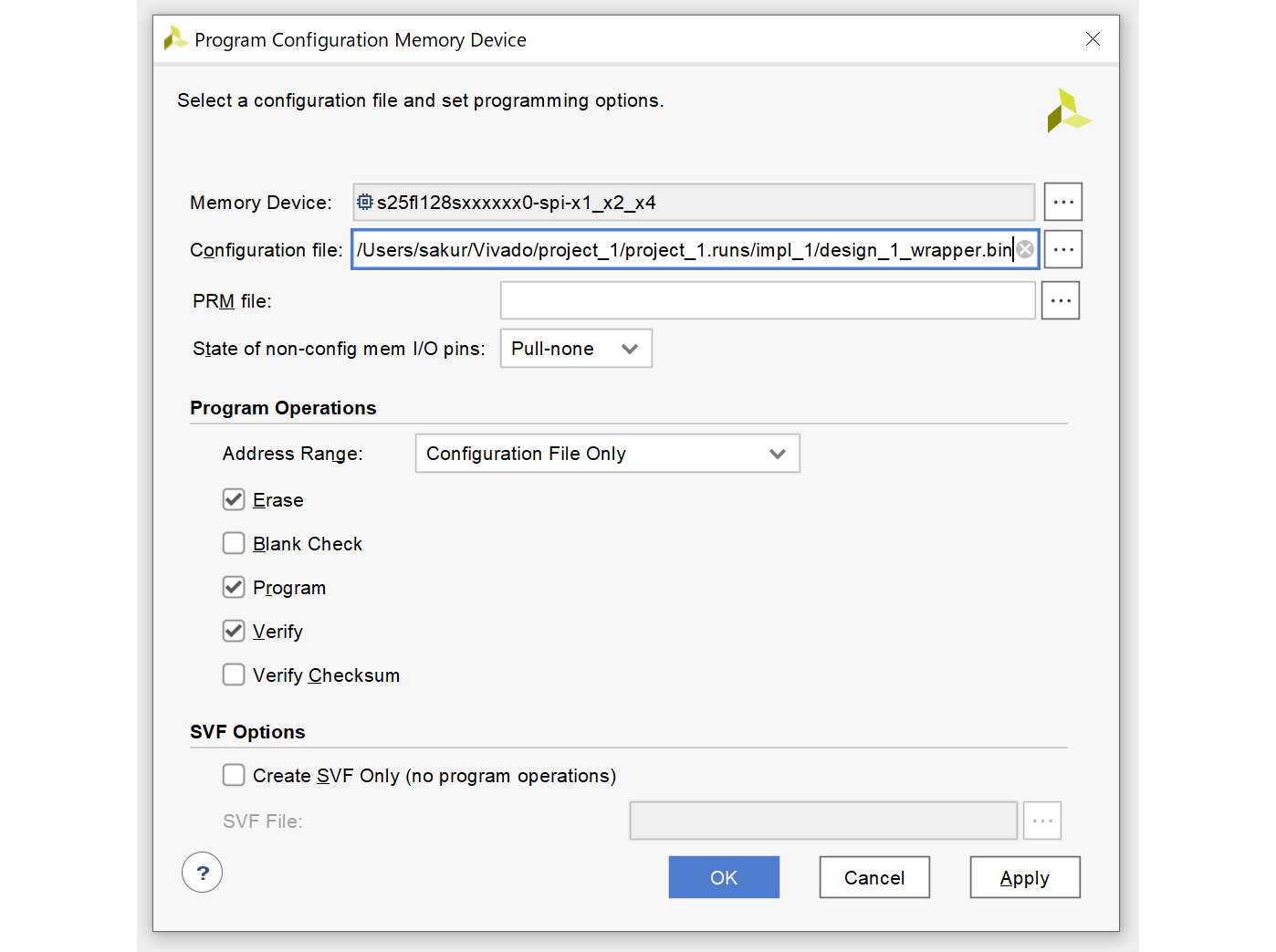

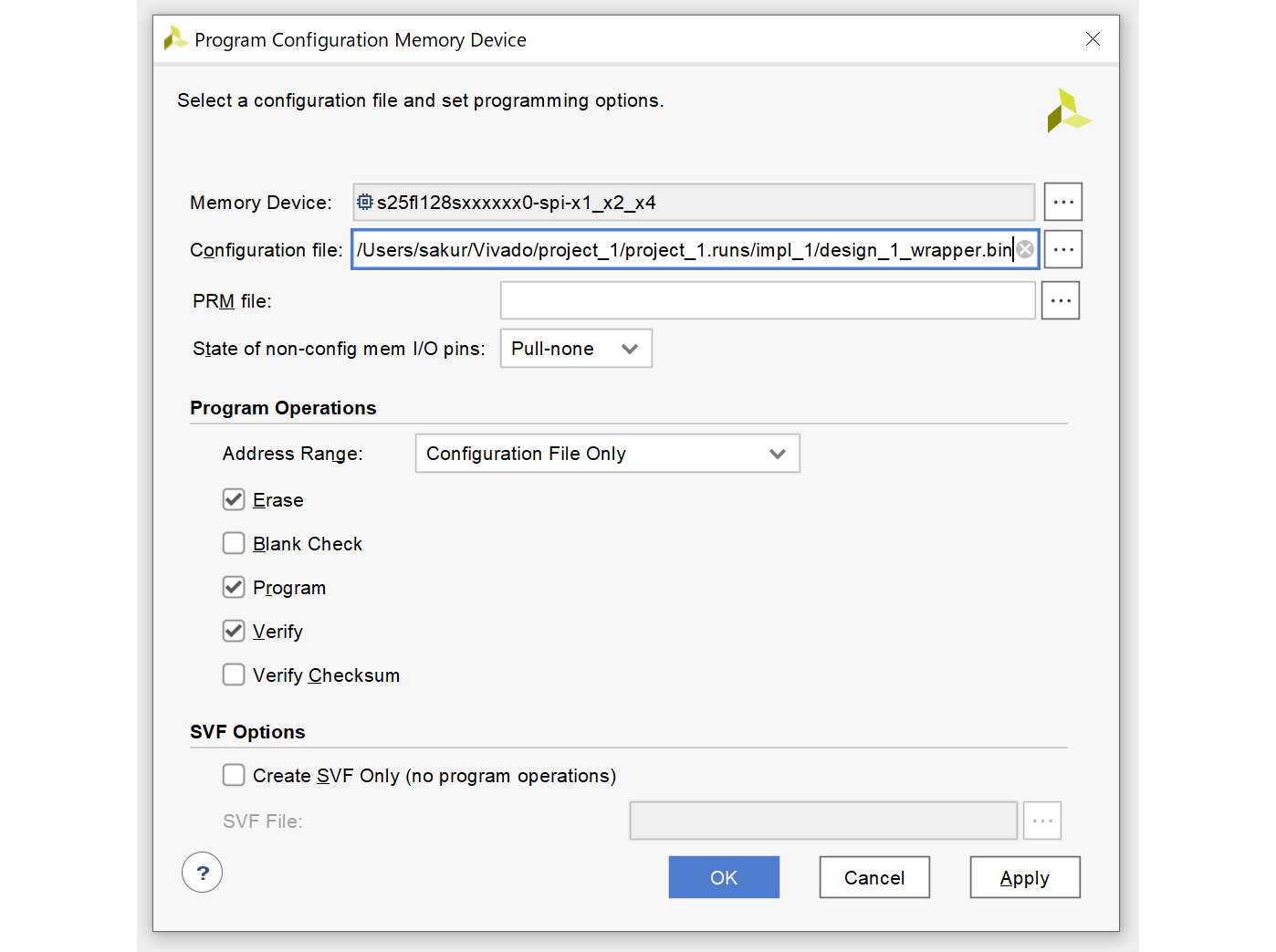

このように、JTAGのデバイスを右クリックすると、メニューが現れるので、Program Configuration Memory Deviceをクリックします。すると次の画面が出るので、デバイスを選択し、プログラミングします。

図410.2

図410.2

前のブログ

次のブログ

前のブログ

次のブログ